## Lecture Notes in Computer Science

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

2989

## Springer Berlin

Berlin Heidelberg New York Hong Kong London Milan Paris Tokyo Susanne Graf Laurent Mounier (Eds.)

# Model Checking Software

11th International SPIN Workshop Barcelona, Spain, April 1-3, 2004 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Susanne Graf Laurent Mounier VERIMAG 2, avenue de Vignate, 38610 Grenoble-Gières, France E-mail: {Susanne.Graf, Laurent.Mounier}@imag.fr

Library of Congress Control Number: 2004102408

CR Subject Classification (1998): F.3, D.2.4, D.3.1, D.2

ISSN 0302-9743 ISBN 3-540-21314-7 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag is a part of Springer Science+Business Media springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin, Protago-TeX-Production GmbH Printed on acid-free paper SPIN: 10994757 06/3142 5 4 3 2 1 0

#### **Preface**

Since 1995, when the SPIN workshop series was instigated, SPIN workshops have been held on an annual basis in Montréal (1995), New Brunswick (1996), Enschede (1997), Paris (1998), Trento (1999), Toulouse (1999), Stanford (2000), Toronto (2001), Grenoble (2002) and Portland (2003). All but the first SPIN workshop were organized as satellite events of larger conferences, in particular of CAV (1996), TACAS (1997), FORTE/PSTV (1998), FLOC (1999), the World Congress on Formal Methods (1999), FMOODS (2000), ICSE (2001, 2003) and ETAPS (2002). This year again, SPIN was held as a satellite event of ETAPS 2004. The co-location of SPIN workshops with conferences has proven to be very successful and has helped to disseminate SPIN model checking technology to wider audiences. Since 1999, the proceedings of the SPIN workshops have appeared in Springer-Verlag's Lecture Notes in Computer Science series.

The history of successful SPIN workshops is evidence for the maturing of model checking technology, not only in the hardware domain, but increasingly also in the software area. While in earlier years algorithms and tool development around the SPIN model checker were the focus of this workshop series, for several years now the scope has been widened to include more general approaches to software model checking techniques and tools as well as applications.

The SPIN workshop has become a forum for all practitioners and researchers interested in model checking based techniques for the validation and analysis of communication protocols and software systems. Techniques based on explicit representations of state spaces, as implemented for example in the SPIN model checker or other tools, or techniques based on combinations of explicit representations with symbolic representations, are the focus of this workshop. It has proven to be particularly suitable for analyzing concurrent asynchronous systems. The workshop topics include theoretical and algorithmic foundations and tools, model derivation from code and code derivation from models, techniques for dealing with large and infinite state spaces, timing and applications. The workshop aims to encourage interactions and exchanges of ideas with all related areas in software engineering.

Papers went through a rigorous reviewing process. Each submitted paper was reviewed by three program committee members. Of 48 submissions, 19 research papers and 3 tool presentations were selected. Papers for which one of the editors was a co-author were handled by a sub-committee chaired by Gerard Holzmann.

In addition to the refereed papers, four invited talks were given; of these three were ETAPS invited speakers: Antti Valmari (Tampere, Finland) on the Rubik's Cube and what it can tell us about data structures, information theory and randomization, Mary-Lou Soffa (Pittsburgh, USA) on the foundations of code optimization, and Robin Milner (Cambridge, UK) on the grand challenge of building a theory for global ubiquitous computing. Finally, the SPIN invited

speaker Reinhard Wilhelm (Saarbrücken, Germany) gave a talk on the analysis of timing models by means of abstract interpretation.

This year we took up an initiative started in 2002 and solicited tutorials that provided opportunities to get detailed insights into some validation tools and the methodologies of their use. Out of 3 submissions, the program committee selected 2 tutorials.

- An "advanced SPIN tutorial" giving an overview of recent extensions of the SPIN model checker as well as some methodological advice for its use. It was mainly addressed to users who want to use SPIN as a modelling and validation environment.

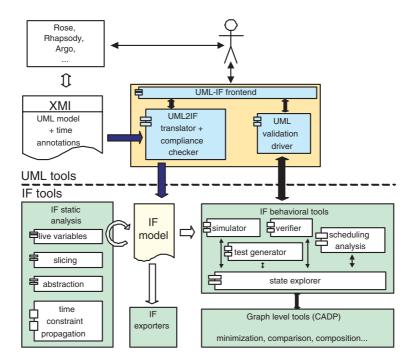

- A tutorial on the IF validation environment providing an overview of the IF modelling language and the main functionalities of the validation toolbox.

It was addressed to users who want to use IF as a validation environment by feeding it with models in the IF language, or in SDL or UML, but also to tool developers who would like to interface their tools with the IF environment.

Acknowledgements. The volume editors wish to thank all members of the program committee as well as the external reviewers for their tremendous effort that led to the selection of this year's program. We furthermore wish to thank the organizers of ETAPS 2004 for inviting us to hold SPIN 2004 as a satellite event and for their support and flexibility in accommodating the particular needs of the SPIN workshop. We wish to thank in particular Fernando Orejas and Jordi Cortadella. Finally, we wish to thank Springer-Verlag for providing us with the possibility to use a conference online service free of charge, and the METAFrame team, in particular Martin Karusseit, for their very valuable and reactive support.

January 2004

Susanne Graf Laurent Mounier

## Organization

SPIN 2004 was the 11th instance of the SPIN workshop on Model Checking of Software. It was held in cooperation with ACM SIGPLAN as a satellite event of ETAPS 2004, the European Joint Conferences on Theory and Practice of Software, which was organized by the Technical University of Catalonia in Barcelona, Spain.

### **Advisory Committee**

Gerard Holzmann Amir Pnueli

#### Steering Committee

Thomas Ball Susanne Graf Stefan Leue Moshe Vardi

Pierre Wolper (chair)

#### **Program Committee**

Chairs: Susanne Graf (VERIMAG, Grenoble)

Laurent Mounier (VERIMAG, Grenoble)

Bernard Boigelot (Liège, Belgium) Dragan Bošnački (Eindhoven, Netherlands) David Dill (Stanford, USA) Javier Esparza (Stuttgart, Germany) Patrice Godefroid (Bell Labs, USA) Susanne Graf (Grenoble, France) John Hatcliff (Kansas State, USA) Gerard Holzmann (NASA/JPL, USA) Stefan Leue (Freiburg, Germany) Pedro Merino (Malaga, Spain) Laurent Mounier (Grenoble, France) Mooly Sagiv (Tel Aviv, Israel) Scott Stoller (Stony Brook, USA) Antti Valmari (Tampere, Finland)

#### Reviewers

Robby

Suzana Andova

Gerd Behrmann

Saddek Bensalem

Marius Bozga

Cas Cremers

Maria del Mar Gallardo

Manuel Diaz

Jürgen Dingel

Jean-Claude Fernandez

Jaco Geldenhuys

Keijo Heljanko

Radu Iosif

Natalia Ioustinova

Rajeev Joshi

Tommi Junttila

Antero Kangas

Timo Karvi

Barbara König

Yassine Lakhnech

Johan Lilius

Jesus Martinez

Richard Mayr

Iulian Ober

Shaham Ohad Michael Périn Ilya Shlyakhter Stavros Tripakis Jaco van de Pol Kimmo Varpaaniemi Wei Wei Tim Willemse Eran Yahav

Ping Yang Greta Yorsh

## **Table of Contents**

| Invited Paper                                                                   |     |

|---------------------------------------------------------------------------------|-----|

| Formal Analysis of Processor Timing Models                                      | 1   |

| Heuristics and Probabilities                                                    |     |

| Typical Structural Properties of State Spaces                                   | 5   |

| State Caching Reconsidered                                                      | 23  |

| Directed Error Detection in C++ with the Assembly-Level Model Checker StEAM     | 39  |

| Fast and Accurate Bitstate Verification for SPIN                                | 57  |

| Improvements of SPIN                                                            |     |

| Model-Driven Software Verification                                              | 76  |

| Minimization of Counterexamples in SPIN                                         | 92  |

| Validation of Timed Systems                                                     |     |

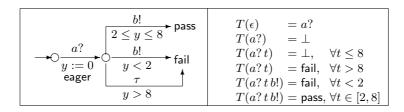

| Black-Box Conformance Testing for Real-Time Systems                             | 109 |

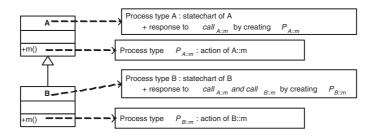

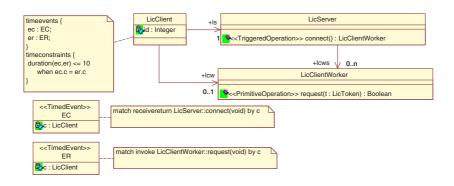

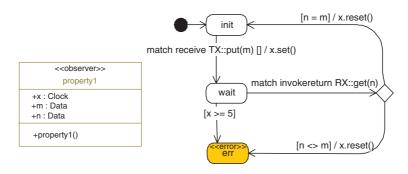

| Validation of UML Models via a Mapping to Communicating Extended Timed Automata | 127 |

| Tool Papers                                                                     |     |

| Explicit State Model Checking with Hopper                                       | 146 |

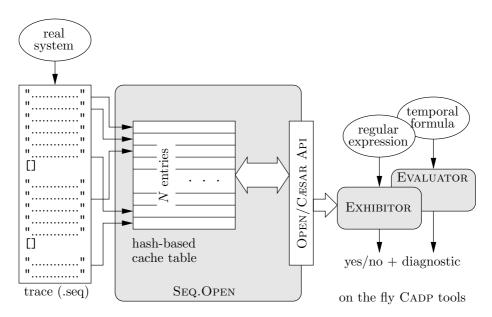

| SEQ.OPEN: A Tool for Efficient Trace-Based Verification                         | 151 |

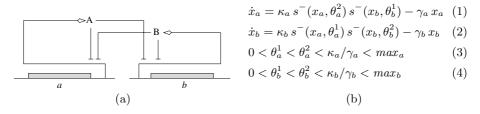

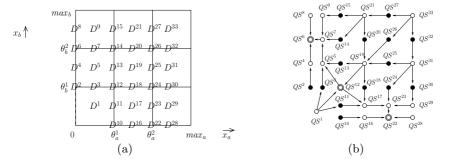

| $ \begin{array}{c} \text{Model Checking Genetic Regulatory Networks Using GNA and CADP} \\ \text{Gr\'egory Batt, Damien Bergamini, Hidde de Jong, Hubert Garavel,} \\ \text{Radu Mateescu} \end{array} $ | 158 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Abstraction and Symbolic Methods                                                                                                                                                                         |     |

| Verification of Java Programs Using Symbolic Execution and Invariant Generation                                                                                                                          | 164 |

| Polynomial Time Image Computation with Interval-Definable Counters Systems                                                                                                                               | 182 |

| Using Fairness to Make Abstractions Work                                                                                                                                                                 | 198 |

| A Scalable Incomplete Test for Message Buffer Overflow in Promela Models                                                                                                                                 | 216 |

| Applications                                                                                                                                                                                             |     |

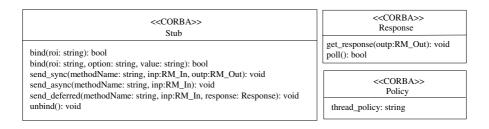

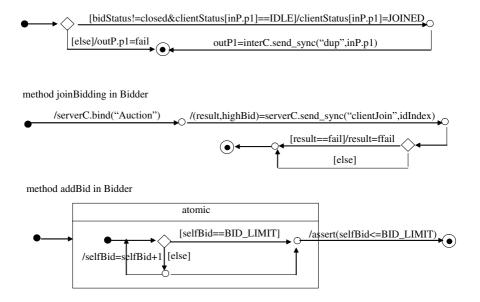

| Translation from Adapted UML to Promela for CORBA-Based Applications                                                                                                                                     | 234 |

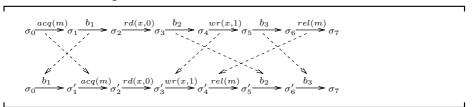

| Verifying Commit-Atomicity Using Model-Checking                                                                                                                                                          | 252 |

| Analysis of Distributed Spin Applied to Industrial-Scale Models                                                                                                                                          | 267 |

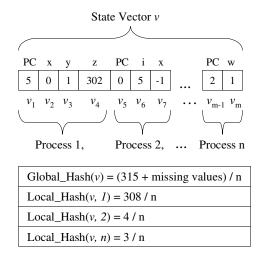

| Verification of MPI-Based Software for Scientific Computation Stephen F. Siegel, George S. Avrunin                                                                                                       | 286 |

| Tutorials                                                                                                                                                                                                |     |

| Advanced SPIN Tutorial                                                                                                                                                                                   | 304 |

| IF Validation Environment Tutorial                                                                                                                                                                       | 306 |

| Author Index                                                                                                                                                                                             | 309 |

## Formal Analysis of Processor Timing Models

Reinhard Wilhelm\*

Informatik Universität des Saarlandes Saarbrücken

Abstract. Hard real-time systems need methods to determine upper bounds for their execution times, usually called worst-case execution times. This talk gives an introduction into state-of-art Timing-Analysis methods. These use Abstract Interpretation to predict the system's behavior on the underlying processor's components and Integer Linear Programming to determine a worst-case path through the program. The abstract interpretation is based on an abstract processor model that is conservative with respect to the timing behavior of the concrete processor. Ongoing work is reported to analyze abstract processor models for properties that have a strong influence on the expected precision of timing prediction and also on the architecture of the timing-analysis tool. Some of the properties we are interested in can be model checked.

#### 1 WCET Determination

Hard real-time systems need methods to determine upper bounds for their execution times, usually called worst-case execution times, (WCET). Based on these bounds, a schedulability analysis can check whether the underlying hardware is fast enough to execute the system's task such that they all finish before their deadlines. This problem is nontrivial because performance-enhancing architectural features such as caches, pipelines, and branch prediction introduce "local non-determinism" into the processor behavior; local inspection of the program can not determine what the contribution of an instruction to the program's overall execution time is. The execution history determines whether the instruction's memory accesses hit or miss the cache, whether the pipeline units needed by the instruction are occupied or not, and whether branch prediction is correct or not.

#### 2 Tool Architecture

State-of-art Timing-Analysis methods split the task into (at least) two subtasks, the prediction of the task's behavior on the processor components such as caches and pipelines, formerly called "micro-architecture modeling" [HBW94], and the determination of a worst-case path. They use Abstract Interpretation to predict

<sup>\*</sup> Work reported herein is supported by the Transregional Collaborative Research Center AVACS of the Deutsche Forschungsgemeinschaft.

S. Graf and L. Mounier (Eds.): SPIN 2004, LNCS 2989, pp. 1-4, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

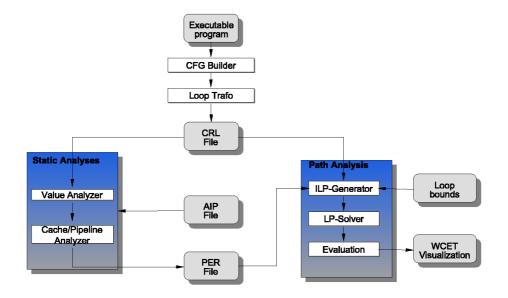

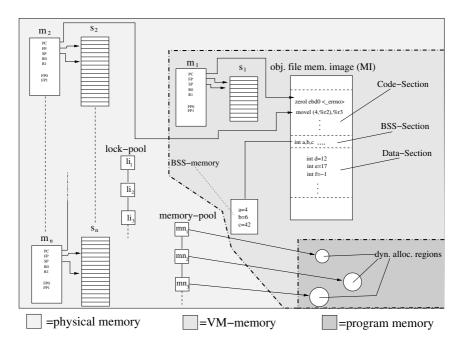

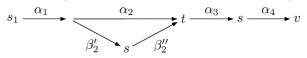

the system's behavior on the underlying processor's components and Integer Linear Programming to determine a worst-case path through the program [LMW99]. A typical tool architecture is the one of aiT, the tool developed and marketed by AbsInt Angewandte Informatik in Saarbrücken, cf. Fig. 1.

Fig. 1. Architecture of the aiT WCET analysis tool

The articles [FHL<sup>+</sup>01,LTH02] report on WCET tool developments for complex processor architectures, namely the Motorola ColdFire 5307 and the Motorola PowerPC 755. These were the first fully covered complex processors.

## 3 Timing Anomalies

The architecture of WCET-tools and the precision of the results of WCET analyses strongly depend on the architecture of the employed processor [HLTW03]. Out-of-order execution and control speculation introduce interferences between processor components, e.g. caches, pipelines, and branch prediction units. These interferences forbid modular designs of WCET tools, which would execute the subtasks of WCET analysis consecutively. Instead, complex integrated designs are needed resulting in high demand for space and analysis time.

In the following, several such properties of processor architectures are described. They cause the processor to display what is called *Timing Anomalies* [Lun02]. Timing anomalies are contra-intuitive influences of the (local) execution time of one instruction on the (global) execution time of the whole program. The interaction of several processor features can interact in such a way

that a locally faster execution of an instruction can lead to a globally longer execution time of the whole program. This is only the first case of a timing anomaly. The general case is the following. Different assumption about the processor's execution state, e.g. the fact that the instruction is or is not in the instruction cache, will result in a difference  $\Delta T_1$  of the execution time of the instruction between these two cases. Either assumption may lead to a difference  $\Delta T$  of the global execution time compared to the other one. We say that a timing anomaly occurs if either

$\Delta T_1 < 0$  i.e., the instruction executes faster, and

$\Delta T < \Delta T_1$  , the overall execution is accelerated by more than the acceleration of the instruction, or

$\Delta T > 0$ , the program runs longer than before.

$\Delta T_1 > 0$  i.e., the instruction takes longer to execute, and

$\Delta T > \Delta T_1$  i.e., the overall execution is extended by more than the delay of the instruction, or

$\Delta T < 0$  i.e., the overall execution is the program takes less time to execute than before.

The case  $\Delta T_1 < 0 \land \Delta T > 0$  is a critical case for WCET analysis. It makes it impossible to use local worst case scenarios for WCET computation. This necessitates a conservative, i.e., upper approximation to the damages potentially caused by all cases or forces the analysis to follow all possible scenarios.

Unfortunately, as [LS99,Lun02] have observed, the worst case penalties imposed by a timing anomaly may not be bounded by an architecture-dependent, but program-independent constant, but may depend on the program size. This is the so-called *Domino Effect*. This domino effect was shown to exist for the Motorola PowerPC 755 in [Sch03].

## 4 Formal Analysis of Processor Timing Models

The abstract-interpretation-based timing analysis is based on abstract processor models that are conservative with respect to the timing behavior of the concrete processors. To prove this is a major endeavor to be undertaken in the Transregional Collaborative Research Center AVACS. Another line of research is the derivation of processor timing models from formal specifications in VHDL or Verilog.

We are currently applying formal analysis of timing models to check for relevant properties, e.g., use model checking to detect timing anomalies and domino effects or their absence, resp. Bounded model checking can be used to check for the existence of upper bounds on the damage done by one processor component onto the state of another one, e.g. the damage of a branch misprediction to the instruction cache by loading superfluous instructions. The bound can be computed from architectural parameters, such as the depth of the pipeline and the length of prefetch queues.

**Acknowledgements.** Thanks go to Stephan Thesing for clarifications about timing anomalies.

#### References

- [FHL<sup>+</sup>01] C. Ferdinand, R. Heckmann, M. Langenbach, F. Martin, M. Schmidt, H. Theiling, S. Thesing, and R. Wilhelm. WCET Determination for a Real-Life Processor. In T.A. Henzinger and C. Kirsch, editors, *Embedded Software*, volume 2211 of *Lecture Notes in Computer Science*, pages 469 – 485. Springer, 2001.

- [HBW94] Marion G. Harmon, T.P. Baker, and David B. Whalley. A Retargetable Technique for Predicting Execution Time of Code Segments. Real-Time Systems, 7:159–182, 1994.

- [HLTW03] Reinhold Heckmann, Marc Langenbach, Stephan Thesing, and Reinhard Wilhelm. The influence of processor architecture and the design and the results of WCET tools. *IEEE Proceedings on Real-Time Systems*, 91(7):1038–1054, July 2003.

- [LMW99] Yau-Tsun Steven Li, Sharad Malik, and Andrew Wolfe. Performance estimation of embedded software with instruction cache modeling. *Design Automation of Electronic Systems*, 4(3):257–279, 1999.

- [LS99] Thomas Lundqvist and Per Stenström. Timing anomalies in dynamically scheduled microprocessors. In *Proceedings of the 20th IEEE Real-Time Systems Symposium (RTSS'99)*, pages 12–21, December 1999.

- [LTH02] M. Langenbach, S. Thesing, and R. Heckmann. Pipeline Modelling for Timing Analysis. In Static Analysis Symposium, volume 2274 of LNCS, pages 294–309. Springer Verlag, 2002.

- [Lun02] Thomas Lundqvist. A WCET Analysis Method for Pipelined Microprocessors with Cache Memories. PhD thesis, Chalmers University of Technology, Göteborg, Sweden, 2002.

- [Sch03] Joern Schneider. Combined Schedulability and WCET Analysis for Real-Time Operating Systems. PhD thesis, Saarland University, 2003.

## Typical Structural Properties of State Spaces

Radek Pelánek\*

Department of Computer Science, Faculty of Informatics Masaryk University Brno, Czech Republic xpelanek@fi.muni.cz

**Abstract.** Explicit model checking algorithms explore the full state space of a system. We have gathered a large collection of state spaces and performed an extensive study of their structural properties. The results show that state spaces have several typical properties and that they differ significantly from both random graphs and regular graphs. We point out how to exploit these typical properties in practical model checking algorithms.

#### 1 Introduction

Model checking is an automatic method for formal verification of systems. In this paper we focus on explicit model checking which is the state-of-the-art approach to verification of asynchronous models (particularly protocols). This approach explicitly builds the full  $state\ space$  of the model (also called Kripke structure, occurrence or reachability graph). The state space represents all (reachable) states of the system and transitions among them. The state space is used to check specifications expressed in a suitable temporal logic. The main obstacle of model checking is  $state\ explosion\ —$  the size of the state space grows exponentially with the size of the model description. Hence, model checking has to deal with extremely large graphs.

The classical model for large unstructured graphs is the  $random\ graph$  model of Erdős and Renyi [11]. In this model every pair of nodes is connected with an edge with a given probability p. Large graphs are studied in many diverse areas, such as social sciences (networks of acquaintances), biology (food webs, protein interaction networks), geography (river networks), and computer science (Internet traffic, world wide web). Recent extensive studies of these graphs revealed that they share many common structural properties and that these properties differ significantly from properties of random graphs. This observation led to the development of more accurate models for large graphs occurring in practice (e.g., 'small worlds' and 'scale-free networks' models) and to a better understanding of processes in these networks. For example, it improved the understanding of the spread of diseases and vulnerability of computer networks to attacks; see Barabasi [2] and Watts [32] for a high-level overview of this research and further references.

<sup>\*</sup> Supported by GA ČR grant no. 201/03/0509

S. Graf and L. Mounier (Eds.): SPIN 2004, LNCS 2989, pp. 5-22, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

In model checking, we usually treat state spaces as arbitrary graphs. However, since state spaces are generated from short descriptions, it is clear that they have some special properties. This line of thought leads to the following questions:

- 1. What do state spaces have in common? What are their typical properties?

- 2. Can state spaces be modeled by random graphs or by some class of regular graphs in a satisfactory manner?

- 3. Can we exploit these typical properties to traverse or model check a state space more efficiently? Or at least to better analyze complexity of algorithms? Can some information about a state space be of any use to the user or to the developer of a model checker?

- 4. Is there any significant difference between toy academical models and real life case studies? Are state spaces similar to such an extent that it does not matter which models we choose for benchmarking our algorithms?

Methodology. The basic approach is the following: we measure many graph parameters of a large collection of state spaces and try to draw answers from the results. We restrict ourselves to asynchronous models, because these are typically investigated by explicit model checkers. We consider neither labels on edges nor atomic propositions in states and thus we focus only on structural properties of graphs. For generating state spaces we have used four well-known model checkers (SPIN [22], CADP [14], Murphi [10],  $\mu$ CR [16]L) and two experimental model checkers. In all, we have used 55 different models including many large case studies (see Appendix A). In this report we summarize our observations, point out possible applications, and try to outline some answers. The project's web page [1] contains more details about investigated state spaces and the way in which they were generated. Moreover, interested reader can find on the web page all state spaces in a simple textual format together with a detailed report for each of them, summary tables for each measured parameter, and more summary statistics and figures.

Related work. Many authors point out the importance of the study of models occurring in practice (e.g., [13]). But to the best of our knowledge, there has been no systematic work in this direction. In many articles one can find remarks and observation concerning typical values of individual parameters, e.g., diameter [5, 28], back level edges [31,3], degree, stack depth [20]. Some authors make implicit assumptions about the structure of state spaces [7,23] or claim that the usefulness of their approach is based on characteristics of state spaces without actually identifying these characteristics [30]. Groote and van Ham [17] try to visualize large state spaces with the goal of providing the user with better insight into a model.

Organization of the paper. Section 2 describes studied parameters, results of measurements, their analysis, and possible application. Section 3 compares different classes of state spaces. An impatient reader can jump directly to Section 4 where our observations are summarized and where we provide some answers. Finally, the last section outlines several new questions for future research.

#### 2 Parameters of State Spaces

A state space is a relational structure which represents the behavior of a system (program, protocol, chip, ...). It represents all possible states of the system and transitions between them. Thus we can view a state space as a simple directed graph  $G = (V, E, v_0)$  with a set of vertices V, a set of directed edges  $E \subseteq V \times V$ , and a distinguished initial vertex  $v_0$ . Moreover, we suppose that all vertices are reachable from the initial one. In the following we use graph when talking about generic notions and state space when talking about notions which are specific to state spaces of asynchronous models.

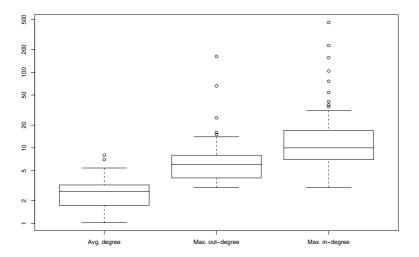

#### 2.1 Degrees

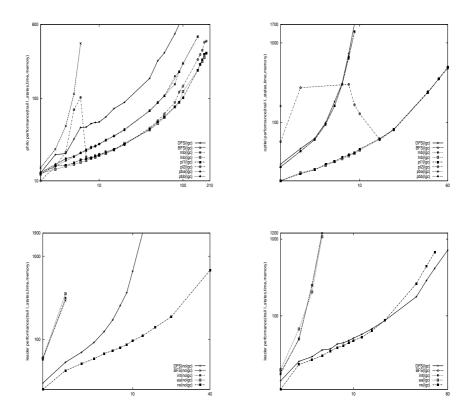

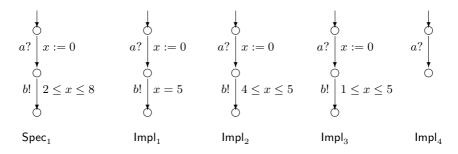

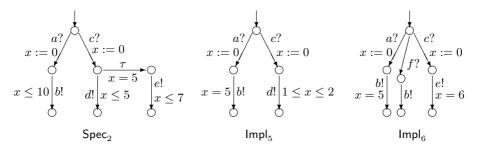

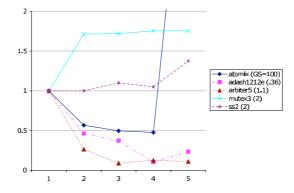

Out-degree (in-degree) of a vertex is the number of edges leading from (to) this vertex. Average degree is just |E|/|V|. The basic observation is that the average degree is very small – typically around 3 (Fig. 1). Maximal in-(out-)degree is often several times higher than the average degree but with respect to the size of the state space it is small as well. Hence state spaces do not contain any 'hubs'. In this respect state spaces are similar to random graphs, which have Poisson distribution of degrees. On the other hand, scale free networks discussed in the introduction are characterized by the power-law distribution of degrees and the existence of hubs is a typical feature of such networks [2].

The fact that state spaces are sparse is not surprising and was observed long ago<sup>2</sup>. It can be quite easily explained: the degree corresponds to a 'branching factor' of a state; the branching is due to parallel components of the model and due to the inner nondeterminism of components; and both of these are usually very small. In fact, it seems reasonable to claim that in practice  $|E| \in O(|V|)$ . Nevertheless, the sparseness is usually not taken into account either in the construction of model checking algorithms or in the analysis of their complexity.

In many cases the average degree is even smaller than two, since there are many vertices with degree one. This observation can be used for saving some memory during the state space traversal [4].

#### 2.2 Strongly Connected Components

A strongly connected component (SCC) of G is a maximal set of states  $C \subseteq V$  such that for each  $u, v \in C$ , the vertex v is reachable from u and vice versa. The quotient graph of G is a graph (W, H) such that W is the set of the SCCs of G and  $(C_1, C_2) \in H$  if and only if  $C_1 \neq C_2$  and there exist  $r \in C_1$ ,  $s \in C_2$  such that  $(r, s) \in E$ . The SCC quotient height of the graph G is the length of the longest

<sup>&</sup>lt;sup>1</sup> We consider state spaces as simple graphs, i.e., we do not consider self-loops and multiedges. Although these may be significant for model checking temporal logics, they are not that important for the structural properties we consider here.

<sup>&</sup>lt;sup>2</sup> Holzman [20] gives an estimate 2 for average degree.

**Fig. 1.** Degree statistics. Values are displayed with the boxplot method. The upper and lower lines are maximum and minimum values, the middle line is a median, the other two are quartiles. Circles mark outliers. Note the logarithmic *y*-axis.

path in the quotient graph of G. A component is trivial if it contains only one vertex. Finally, a component is terminal if it has no successor in the quotient graph.

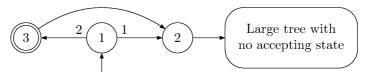

For state spaces, the height of the SCC quotient graph is small. In all but one case it is smaller than 200, in 70% of cases it is smaller than 50. The structure of quotient graph has one of the following types:

- there is only one SCC component (18% of cases),

- there are only trivial components (the graph is acyclic) (14\% of cases),

- there is one large component which contains most states; the largest component is usually terminal and often it is even the only terminal.

The number of SCCs can be very high, but this is mainly due to trivial components. The conclusion is that most states lie either in the largest component or in some trivial component and that the largest component tends to be 'at the bottom' of the SCC quotient graph.

SCCs play an important role in many model checking algorithms and the above stated observation can be quite significant with respect to practical applicability of some approaches, for example:

The runtime of symbolic SCC decomposition algorithms [12,25] depends very much on the structure of the SCC quotient graph. The thorough analysis [27] shows that the complexity of these algorithms depends on the SCC quotient height, the number of SCC, and the number of nontrivial SCC. We note that symbolic algorithms are usually used for synchronous models (whereas our state spaces correspond to asynchronous ones) and thus our observations are not directly applicable here. However, the distributed explicit cycle detection algorithm [6] has complexity proportional to the SCC quotient height as well.

- The existence of one large component shows the limited applicability of some algorithms. The 'sweep line' method [8] of the state space exploration saves memory by deleting states which are in a fully explored SCC. The distributed cycle detection based on partitioning the state space with respect to SCCs [23] assigns to each computer in a network one or more SCCs.

- On the other hand, some algorithms could be simpler for state spaces which

have one big component. For example during random walk there is a little

danger that the algorithm will stuck in some small component.

#### 2.3 Properties of Breadth-First and Depth-First Search

The basic model checking procedure is a reachability analysis – searching a state space for an error state. Here we consider two basic methods for state space traversal and their properties.

**Breadth-First Search (BFS).** Let us consider the BFS from the initial vertex  $v_0$ . A level of the BFS with an index k is a set of states with distance from  $v_0$  equal to k. The BFS height is the largest index of a non-empty level. An edge (u, v) is a back level edge if v belongs to a level with a lower or the same index as u. The length of a back level edge is the difference between the indices of the two levels.

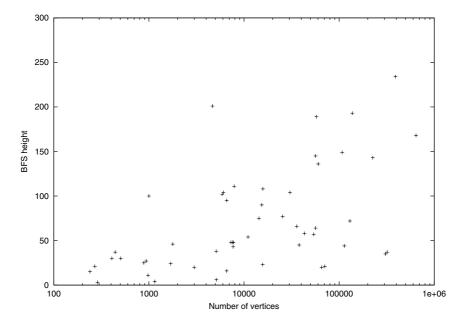

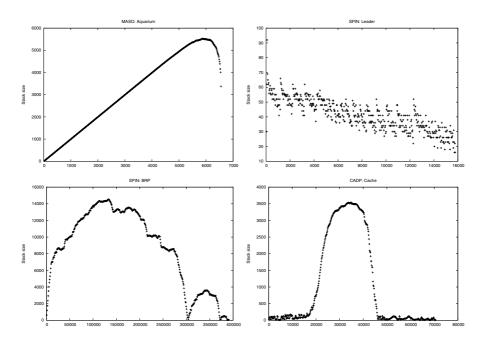

- The BFS height is small (Fig. 2). There is no clear correlation between the state space size and the BFS height. It depends rather on the type of the model.

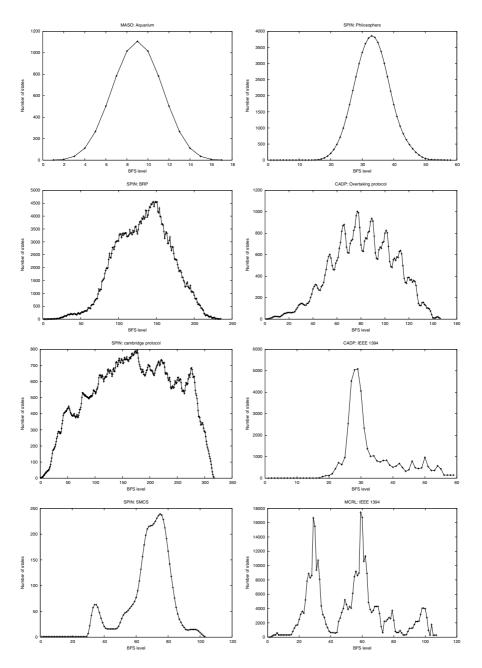

- The sizes of levels follow a typical pattern. If we plot the number of states on a level against the index of a level we get a BFS level  $graph^3$ . See Fig. 3 for several such graphs. Usually this graph has a 'bell-like' shape.

- The relative number of back level edges is (rather uniformly) distributed between 0% and 50%. Most edges are local they connect two close levels (as already observed by Tronci et al. [31]). However, for most models there exist some long back level edges. For exact results and statistics see [1].

- For most systems we observe that there are only a few typical lengths of back level edges and that most back level edges have these lengths. This is probably caused by the fact that back level edges correspond to jumps in the model. There are typically only a reasonably small number of different jumps in a model.

$<sup>^3</sup>$  Note that the word 'graph' is overloaded here. In this context we mean graph in the functional sense.

Fig. 2. The BFS height plotted against the size of the state space. Note the logarithmic x-axis. Three examples have height larger than 300.

- Tronci et al. [31,24] exploit locality of edges for state space caching. Their technique stores only recently visited states. The efficiency (and termination) of their algorithm rely on the fact that most edges are local and hence target states of edges are usually in the cache. In a similar way, one could exploit typical lengths of back level edges or try to estimate the maximal length of a back level edge and use this estimate as a key for removing states from the cache.

- The algorithm for distributed cycle detection by Barnat et al. [3] has complexity proportional to the number of back level edges.

- The typical shape of the BFS level graph can be exploited for a prediction of the size of a state space. Particularly, when a model checker runs out of memory it may be useful to see the BFS level graph it can help the user to decide, whether it will be sufficient just to use a more powerful computer (or a distributed computation on several computers) or whether the model is hopelessly big and it is necessary to use some reduction and/or abstraction. This is easy to implement (and add to existing model checkers) and in our experience it can be very useful to the user.

**Depth-First Search (DFS).** Next we consider the depth-first search from the initial vertex. The behavior of DFS (but not the completeness) depends on the

**Fig. 3.** BFS level graphs. For simple models the curve is really smooth and bell-like. For more complex models it can be a bit ragged. The last two graphs show that there are exceptions which have more 'peaks' (but these are rare exceptions).

order in which successors of each vertex are visited. Therefore we have considered several runs of DFS with different orderings of successors.

If we plot the size of the stack during DFS we get a *stack graph*. Fig. 4 shows several stack graphs (for more graphs see [1]). The interesting observation is that the shape of the graph does not depend much on the ordering of successors. The stack graph changes a bit of course, but the overall appearance remains the same. Moreover, each state space has its own typical graph. In contrast, all random graphs have rather the same, smooth stack graph.

When we count the length of cycles encountered during DFS we find out that there are several typical lengths of cycles which occur very often; after the observation of the typical lengths of back level edges this does not come as a great surprise.

These observations point out interesting structural properties of state spaces (and their differences from random graphs) but do not seem to have many direct applications. The only one is the stack cycling technique [21] which exploits the fact that the size of the stack does not change too quickly and stores part of the stack on the magnetic disc. Stack graphs could provide better insight into how to manage this process.

Fig. 4. Stack graphs. The first one is the stack graph of a very simple model. Stack graphs of random graphs are similar to this one. The other three stack graphs correspond to more complex models.

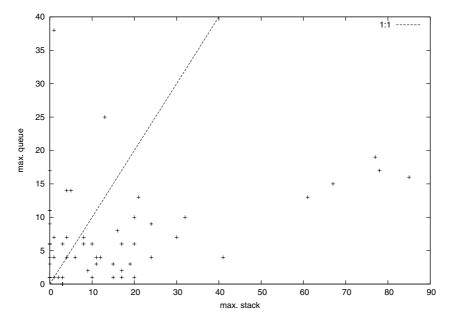

Queue and Stack Size. For implementations of the breadth- and depth-first search one uses queue and stack data structures. These data structures are in most model checkers treated differently from a set of already visited states. This set (usually implemented as a hash table) is considered to be the main memory consumer. Therefore its size is reduced using sophisticated techniques: states are compressed with lossless compression [19] or bit-state hashing [18], stored on magnetic disc [29], or only some states are stored [4,15]. On the other hand, the whole queue/stack is typically kept in memory without any compression. Our measurements show that the sizes of these structures are often as much as 10% of the size of a state space; see Fig. 5 for results and comparison of queue and stack sizes. Thus it may happen that the applicability of a model checker becomes limited by the size of a queue/stack data structure. Therefore it is important to pay attention to these structures when engineering a model checker. We note that this is already done is some model checkers - SPIN can store part of a stack on disc [21], UPPAAL stores all states in the hash table and maintains only references in a queue/stack [9].

Fig. 5. A comparison of maximal queue and stack sizes expressed as percentages of the state space size. Note that the relative size of a queue is always smaller than 40% of the state space size whereas the relative size of a stack can go up to 90% of the state space size.

#### 2.4 Distances

The diameter of a graph is the length of the largest shortest path between two vertices. The girth of a graph is the length of the shortest cycle. Since diameter and girth are expensive to compute<sup>4</sup> we can determine them only for small state spaces.

However, experiments for small graphs reveal that we can compute good estimates of these parameters with the use of the breadth- and depth-first search. The BFS height can be used to estimate the diameter. For most state spaces the diameter is smaller than 1.5 times the BFS height. Note that for general graphs the diameter can be much larger than the BFS height. DFS can be used to estimate the girth – it is not guaranteed to find the shortest cycle but our experience shows that in practice it does.

It is a 'common belief' (only partially supported in some papers) that the diameter is small. Our experiments confirm this belief. In most cases the diameter is smaller than 200, often much smaller<sup>5</sup>. The girth is in most cases smaller than 8.

The fact that the diameter is small is practically very important. Several algorithms (e.g., [28,12,25]) and the bounded model checking approach [5] directly exploit this fact. Moreover, the fact that the diameter is small suggests that many of the very long counterexamples (as produced by some model checkers) are caused by a poor search and not by the inherent complexity of the bug.

#### 2.5 Local Structure

As the next step we try to analyze the local structure of state spaces. In order to do so, we employ some ideas from the analysis of social networks. A typical characteristics of social networks is *clustering* — two friends of one person are friends together with much higher probability than two randomly picked persons. Thus vertices have a tendency to form clusters. This is a significant feature which distinguishes social networks from random graphs.

In state spaces we can expect some form of clustering as well — two successors of a state are more probable to have some close common successor than two randomly picked states. Specifically, state spaces are well-known to contain many 'diamonds'. We try to formalize these ideas and provide some experimental base for them.

- A diamond rooted at  $v_1$  is a quadruple  $(v_1, v_2, v_3, v_4)$  such that  $\{(v_1, v_2), (v_1, v_3), (v_2, v_4), (v_3, v_4)\} \subseteq E$ .

- The k-neighborhood of v is the set of vertices with distance from v smaller or equal to k.

<sup>&</sup>lt;sup>4</sup> In the context of large state spaces even quadratic algorithms are expensive.

<sup>&</sup>lt;sup>5</sup> Diameters of state spaces are very small with respect to their size and to the theoretical worst case. But compared to random graphs or 'small world' networks it is still rather large (the diameter of these graphs is proportional to the logarithm of their size).

The k-clustering coefficient of a vertex v is the ratio of the number of edges to the number of vertices in the k-neighborhood (not counting the v itself). If the clustering coefficient is equal to 1, no vertex in the neighborhood has two incoming edges within this neighborhood. A higher coefficient implies that there are several paths to some vertices within the neighborhood. Random graphs have clustering coefficients close to 1.

The measurements confirm that the local structure of state spaces significantly differ from random graphs (see [1] for more details):

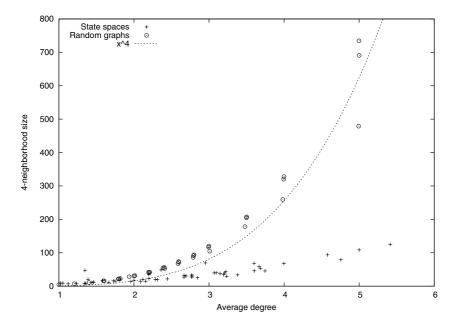

- The size of neighborhood grows much more slowly for state spaces than for random graphs (Fig. 6). This is because the clustering coefficient of state spaces increases (rather linearly) with average degree.

- Diamonds display an interesting dependence on the average degree. For a state space with average degree less than two there are a small number of diamonds. For state spaces with average degree larger than two there are a lot of them.

- Although girth is small for all state spaces, short cycles are abundant only in some graphs — only one third of state spaces have many short cycles.

- The local structure is similar in all parts of a state space.

Fig. 6. Relationship between the size of 4-neighborhood and the average degree, and a comparison with random graphs.

The bottom line of these observations is that the local structure depends very much on the average degree. If the average degree is small then the local structure of the state space is tree-like (without diamonds and short cycles, with many states of degree one). Whereas with the high average degree it has many diamonds and high clustering coefficient. The rather surprising consequence is that the local structure depends on the model only in as much as the average degree does.

This is just the first step in understanding the local structure of state spaces, so it is difficult to give any specific applications. Some of these properties could be exploited by traversal methods which do not store all states [4]. Since the size of a neighborhood grows rather slowly, it might be feasible to do some kind of 'look-ahead' during the exploration of a state space (this is not the case for arbitrary graphs).

#### 3 Comparisons

#### 3.1 Specification Languages and Tools

Most parameters seem to be independent of the specification language used for modeling and the tool used for generating a state space. In fact, the same protocols modeled in different languages yield very similar state spaces. This can be seen as an encouraging result since it says that it is fair to do experimental work with just one model checker.

We have noticed some small differences. For example, Promela models often have sparser state spaces. But because we do not have the same set of examples modeled in all specification languages, we cannot fully support these observations at the moment.

#### 3.2 Toy versus Industrial Examples

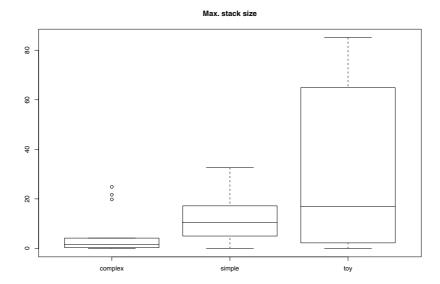

We have manually classified examples into three categories: toy (16), simple (25), and complex (14) (see Appendix A). The major criterion for the classification was the length of the model description. The comparison shows differences in most parameters. Here we only briefly summarize the main trends; more detailed figures can be found on the project's web page [1]:

- The average degree is smaller for state spaces of complex models. This is important because the average degree has a strong correlation with the local structure of the state space (see Section 2.5).

- The maximal size of the stack during DFS is significantly shorter for complex models (Fig. 7).

- The BFS height and the diameter are larger for state spaces of complex models.

- The number of back level edges is smaller for state spaces of complex models but they have longer back level edges.

Fig. 7. The maximal stack size (given in percents of the state space size) during DFS. Results are displayed with the boxplot method (see Fig. 1 for explanation).

Global structure is more regular for state spaces of toy models. This

is demonstrated by BFS level graphs and stack graphs which are much

smoother for state spaces of toy models.

These results stress the importance of having complex case studies in model checking benchmarks. Particularly experiments comparing explicit and symbolic methods are often done on toy examples. Since toy examples have more regular state spaces, they can be more easily represented symbolically.

#### 3.3 Similar Models

We also compared the state spaces of similar models — parametrized models with different values, abstracted models, models with small syntactic change. Moreover, we have compared full state spaces and state spaces reduced with partial order reduction and strong bisimulation.

The resulting state spaces are very similar — most parameters are (nearly) the same or are appropriately scaled with respect to the change in the size of the state space. The exception is that a small syntactic change in a model can sometimes produce a big change of the state space. This occurs mainly in cases where the small change corresponds to some error (or correction) in the model. This suggests that listing state space's parameters could be useful

for users during modeling — the significant change of parameters between two consecutive versions of a model can serve as a warning of a potential error (this can be even done automatically).

#### 4 Conclusions: Answers

Although we have done our measurements on a restricted sample of state spaces, we believe that it is possible to draw general conclusions from the results. We used several different model checkers and models were written by several different users. Results of measurements are consistent — there are no significant exceptions from reported observations.

What are typical properties of state spaces?

State spaces are usually sparse, without hubs, with one large SCC, with small diameter and small SCC quotient height, with many diamond-like structures.

These properties can not be explained theoretically. It is not difficult to construct artificial models without these features. This means that observed properties of state spaces are not the result of the way state spaces are generated nor of some features of specification languages but rather of the way humans design/model systems.

Can state spaces be modeled by random graphs or by some class of regular graphs? State spaces are neither random nor regular. They have some internal structure, but this structure is not strictly regular. This is illustrated by many of our observations:

- local clustering (including diamonds) is completely absent in random graphs

- stack graphs and BFS level graphs are quite structured and ragged, while for both regular and random graphs they are much smoother

- typical values of lengths of back level edges and cycles

- the diameter is larger than for random graphs but small compared to the size of the state space (definitely much smaller than for common regular graphs)

Can we exploit typical properties during model checking?

Typical properties can be useful in many different ways. Throughout the paper we provide several pointers to work that exploits typical values of parameters and we give some more suggestions about how to exploit them.

Values of parameters are not very useful for non-expert users who are not usually aware of what a state space is, but they may be useful for advanced users of the model checker. Properties of the underlying state space can provide users with feedback on their modeling and sanity checks — users can confront obtained parameters with their intuition (particularly useful for SCCs) and compare parameters of similar models, e.g., original and modified model.

The parameter values can be definitively useful for developers of tools, particularly for researchers developing new algorithms — they can help to explain the behavior of new algorithms.

Are there any differences between toy and complex models?

Although state spaces share some properties in common, some can significantly differ. Behavior of some algorithms can be very dependent on the structure of the state space. We can illustrate it on an experiment with random walk. We have performed series of very simple experiments with random walks on generated state spaces. For some graphs one can quickly cover 90% of the state space by random walk, whereas for other we were not able to get beyond 3%. So it is really important to test algorithms on a large number of models before one draws any conclusions.

Particularly, there is a significant difference between state spaces corresponding to complex and toy models. Moreover, we have pointed out that state spaces of similar models are very similar. We conclude that it is not adequate to perform experiments just on few instancies of some toy example<sup>6</sup> and we support calls for a robust set of benchmark examples for model checking [13].

#### 5 Future Work: New Questions

- What more can we say about state spaces when we consider atomic propositions in states (respectively good/bad states)? What is the typical distribution of good/bad states? How many are there? Where are they? What are the properties of product graphs used in LTL model checking (product with Büchi automaton) and branching time logic model checking (game graphs)? Do they have the same properties or are there any significant differences?

- Can we estimate structural properties of a state space from static analysis of its model?

- In this work we consider mainly 'static' properties of state spaces. We have briefly mentioned only the breadth- and depth-first search, but there are many other possible searches and processes over state spaces (particularly random walk and partial searches). What is the 'dynamics' of state spaces?

- What is the effect of efficient modeling [26] on the resulting state space?

- State spaces are quite structured and regular. But how can we capture this regularity exactly? How can we employ this regularity during model checking? Can the understanding of the local structure help us to devise symbolic methods for asynchronous models?

**Acknowledgment.** I thank my supervisor, Ivana Černá, for many valuable discussions and suggestions, and for comments on previous drafts of this paper. Pavel Krčál, Tomáš Hanžl, and other members of the ParaDiSe laboratory have provided useful feedback. Finally, I thank anonymous reviewer for detailed comments.

$<sup>^{6}</sup>$  Thou shalt not do experiments (only) on Philosophers.

#### References

- 1. http://www.fi.muni.cz/~xpelanek/state\_spaces.

- A.L. Barabasi. Linked: How Everything Is Connected to Everything Else and What It Means. Plume, 2003.

- 3. J. Barnat, L. Brim, and J. Chaloupka. Parallel breadth-first search LTL model-checking. In *Proc. Automated Software Engineering (ASE 2003)*, pages 106–115. IEEE Computer Society, 2003.

- G. Behrmann, K.G. Larsen, and R. Pelánek. To store or not to store. In Proc. Computer Aided Verification (CAV 2003), volume 2725 of LNCS, pages 433–445, 2003.

- A. Biere, A. Cimatti, E. Clarke, and Y. Zhu. Symbolic model checking without BDDs. In Proc. Tools and Algorithms for the Construction and Analysis of Systems (TACAS 1999), volume 1579 of LNCS, pages 193–207, 1999.

- I. Černá and R. Pelánek. Distributed explicit fair cycle detection. In Proc. SPIN workshop, volume 2648 of LNCS, pages 49–73, 2003.

- A. Cheng, S. Christensen, and K. H. Mortensen. Model checking coloured petri nets exploiting strongly connected components. In Proc. International Workshop on Discrete Event Systems, pages 169–177, 1996.

- S. Christensen, L.M. Kristensen, and T. Mailund. A Sweep-Line Method for State Space Exploration. In *Proc. Tools and Algorithms for Construction and Analysis* of Systems (TACAS 2001), volume 2031 of LNCS, pages 450–464, 2001.

- 9. A. David, G. Behrmann, K. G. Larsen, and W. Yi. Unification & sharing in timed automata verification. In *Proc. SPIN Workshop*, volume 2648 of *LNCS*, pages 225–229, 2003.

- D. L. Dill, A. J. Drexler, A. J. Hu, and C. Han Yang. Protocol verification as a hardware design aid. In *Proc. Computer Design: VLSI in Computers and Proces*sors, pages 522–525. IEEE Computer Society, 1992.

- 11. P. Erdős and A. Renyi. On random graphs. Publ. Math., 6:290–297, 1959.

- K. Fisler, R. Fraer, G. Kamhi Y. Vardi, and Z. Yang. Is there a best symbolic cycle-detection algorithm? In Proc. Tools and Algorithms for Construction and Analysis of Systems (TACAS 2001), volume 2031 of LNCS, pages 420–434, 2001.

- M. B. Dwyer G. S. Avrunin, J. C. Corbett. Benchmarking finite-state verifiers. International Journal on Software Tools for Technology Transfer (STTT), 2(4):317–320, 2000.

- 14. H. Garavel, F. Lang, and R. Mateescu. An overview of CADP 2001. European Association for Software Science and Technology (EASST) Newsletter, 4:13–24, August 2002.

- P. Godefroid, G.J. Holzmann, and D. Pirottin. State space caching revisited. Formal Methods in System Design, 7(3):227-241, 1995.

- J.F. Groote and A. Ponse. The syntax and semantics of μCRL. In Algebra of Communicating Processes '94, Workshops in Computing Series, pages 26–62, 1995.

- 17. J.F. Groote and F. van Ham. Large state space visualization. In *Proc. of Tools and Algorithms for Construction and Analysis of Systems (TACAS 2003)*, volume 2619 of *LNCS*, pages 585–590, 2003.

- G. J. Holzmann. An analysis of bitstate hashing. In Proc. Protocol Specification, Testing, and Verification, INWG/IFIP, pages 301–314, 1995.

- G. J. Holzmann. State compression in SPIN: Recursive indexing and compression training runs. In Proc. SPIN Workshop. Twente Univ., 1997.

- G.J. Holzmann. Algorithms for automated protocol verification. AT&T Technical Journal. 69(2):32–44, 1990.

- G.J. Holzmann. The engineering of a model checker: the gnu i-protocol case study revisited. In Proc. SPIN Workshop, volume 1680 of LNCS, pages 232–244, 1999.

- G.J. Holzmann. The Spin Model Checker, Primer and Reference Manual. Addison-Wesley, 2003.

- A. L. Lafuente. Simplified distributed LTL model checking by localizing cycles.

Technical Report 176, Institut für Informatik, Universität Freiburg, July 2002.

- G. D. Penna, B. Intrigila, E. Tronci, and M. V. Zilli. Exploiting transition locality in the disk based Murphi verifier. In *Proc. Formal Methods in Computer-Aided Design (FMCAD 2002)*, volume 2517 of *LNCS*, pages 202–219, 2002.

- 25. K. Ravi, R. Bloem, and F. Somenzi. A comparative study of symbolic algorithms for the computation of fair cycles. In *Proc. Formal Methods in Computer-Aided Design (FMCAD 2000)*, volume 1954 of *LNCS*, pages 143–160, 2000.

- Theo C. Ruys. Low-fat recipes for SPIN. In Proc. SPIN Workshop, volume 1885 of LNCS, pages 287–321, 2000.

- F. Somenzi, K. Ravi, and R. Bloem. Analysis of symbolic SCC hull algorithms. In Proc. Formal Methods in Computer-Aided Design (FMCAD 2002), volume 2517 of LNCS, pages 88–105, 2002.

- 28. U. Stern. Algorithmic Techniques in Verification by Explicit State Enumeration. PhD thesis, Technical University of Munich, 1997.

- U. Stern and D. L. Dill. Using magnatic disk instead of main memory in the Murphi verifier. In *Proc. Computer Aided Verification (CAV 1998)*, volume 1427 of *LNCS*, pages 172–183, 1998.

- E. Tronci, G. D. Penna, B. Intrigila, and M. Venturini. A probabilistic approach

to automatic verification of concurrent systems. In *Proc. Asia-Pacific Software*Engineering Conference (APSEC 2001), pages 317–324. IEEE Computer Society,

2001.

- 31. E. Tronci, G. D. Penna, B. Intrigila, and M. V. Zilli. Exploiting transition locality in automatic verification. In *Proc. Correct Hardware Design and Verification Methods* (CHARME 2001), volume 2144, pages 259–274, 2001.

- 32. D. J. Watts. Six Degrees: The Science of a Connected Age. W.W. Norton & Company, 2003.

#### A Models

| Tool   | Model                                 | Type            | Size   |

|--------|---------------------------------------|-----------------|--------|

| Murphi | Peterson's mutual exclusion algorithm | toy             | 882    |

| Murphi | Parallel sorting                      | toy             | 3,000  |

| Murphi | Hardware arbiter                      | $_{\rm simple}$ | 1,778  |

| Murphi | Distributed quering lock              | $_{\rm simple}$ | 7,597  |

| Murphi | Needham-Schroeder protocol            | complex         | 980    |

| Murphi | Dash protocol                         | complex         | 1,694  |

| Murphi | Cache coherence protocol              | complex         | 15,703 |

| Murphi | Scalable coherent interface (SCI)     | complex         | 38,034 |

| Tool             | Model                                        | Type            | Size        |

|------------------|----------------------------------------------|-----------------|-------------|

| SPIN             | Peterson protocol for 3 processes            | toy             | 30,432      |

| SPIN             | Dining philosophers                          | toy             | 54,049      |

| SPIN             | Concurrent sorting                           | toy             | 107,728     |

| SPIN             | Alternating bit protocol                     | simple          | 442         |

| SPIN             | Readers, writers                             | $_{\rm simple}$ | 936         |

| SPIN             | Token ring                                   | $_{\rm simple}$ | 7,744       |

| SPIN             | Snooping cache algorithm                     | simple          | 14,361      |

| SPIN             | Leader election in unidirectional ring       | simple          | 15,791      |

| SPIN             | Go-back-N sliding window protocol            | $_{\rm simple}$ | $35,\!861$  |

| SPIN             | Cambridge ring protocol                      | $_{\rm simple}$ | 162,530     |

| SPIN             | Model of cell-phone handoff strategy         | $_{\rm simple}$ | $225,\!670$ |

| SPIN             | Bounded retransmition protocol               | $_{\rm simple}$ | 391,312     |

| SPIN             | ITU-T multipoint communication service       | complex         |             |

| SPIN             | Flight guidance system                       | complex         | 57,786      |

| SPIN             | Flow control layer validation                | complex         |             |

| SPIN             | Needham-Schroeder public key protocol        | complex         | 307,218     |

| CADP             | Alternating bit                              | simple          | 270         |

| CADP             | HAVi leader election protocol                | $_{\rm simple}$ | 5,107       |

| CADP             | INRES protocol                               | simple          | 7,887       |

| CADP             | Invoicing case study                         | simple          | 16,110      |

| CADP             | Car overtaking protocol                      | simple          | $56,\!482$  |

| CADP             | Philips' bounded retransmission protocol     | simple          | $60,\!381$  |

| CADP             | Directory-based cache coherency protocol     | $_{\rm simple}$ | 70,643      |

| CADP             | Reliable multicast protocol                  | $_{\rm simple}$ | 113,590     |

| CADP             | Cluster file system                          | complex         | 11,031      |

| CADP             | CO4 protocol for distributed knowledge bases | complex         | 25,496      |

| CADP             | IEEE 1394 high performance serial bus        | complex         | 43,172      |

| $\mu \text{CRL}$ | Chatbox                                      | toy             | 65,536      |

| $\mu \text{CRL}$ | Onebit sliding window protocol               | $_{\rm simple}$ | 319,732     |

| $\mu \text{CRL}$ | Modular hef system                           | complex         | 15,349      |

| $\mu \text{CRL}$ | Link layer protocol of the IEEE-1394         | complex         |             |

| $\mu$ CRL        | Distributed lift system                      | complex         | 129,849     |

| Divine           | Cabbage, goat, wolf puzzle                   | toy             | 52          |

| Divine           | Dining philosophers                          | toy             | 728         |

| Divine           | MSMIE protocol                               | simple          | 1,241       |

| Divine           | Bounded retransmition protocol               | simple          | 6,093       |

| Divine           | Alternating bit protocol                     | simple          | 11,268      |

| MASO             | Aquarium example                             | toy             | 6,561       |

| MASO             | Token ring                                   | toy             | 7680        |

| MASO             | Alternating bit protocol                     | toy             | 11,268      |

| MASO             | Adding puzzle                                | toy             | $56,\!561$  |

| MASO             | Elevator                                     | simple          | 643,298     |

## State Caching Reconsidered

Jaco Geldenhuys

Tampere University of Technology, Institute of Software Systems PO Box 553, FIN-33101 Tampere, FINLAND jaco@cs.tut.fi

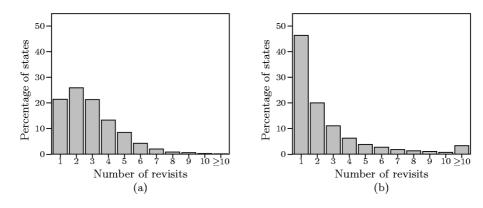

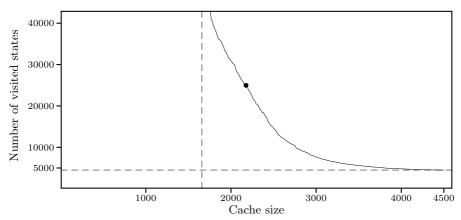

Abstract. State caching makes the full exploration of large state spaces possible by storing only a subset of the reachable states. While memory requirements are limited, the time consumption can increase dramatically if the subset is too small. It is often claimed that state caching is effective when the cache is larger than between 33% and 50% of the total state space, and that random replacement of cached states is the best strategy. Both these ideas are re-investigated in this paper. In addition, the paper introduces a new technique, stratified caching, that reduces time consumption by placing an upper bound on the extra work caused by state caching. This, and a variety of other strategies are evaluated for random graphs and graphs based on actual verification models. Measurements made with Spin are presented.

#### 1 Introduction

Model checking by explicit state enumeration has become increasingly successful in the last decade, but suffers from the well-known state space explosion problem. Techniques for palliating the problem abound, but once the size of a model crosses a certain line, the only hope is a partial search of the state space. While such probabilistic approaches are valuable in detecting violations of the specification, they cannot guarantee correctness; when possible, a full exploration of the state space is, of course, preferable.

This paper focuses on *state caching*, one of the earliest techniques to deal with state space explosion. During state space exploration the reached states are stored in a hash table or similar data structure. When a previously visited state is reached again, it is found among the stored states and does not have to be re-explored. When a new state is generated and the state store is full (i.e., available memory has been exhausted), an already stored state is selected and discarded to make room for the new state. By replacing an old state, the model checker commits itself to re-investigate the state, should it be reached again. This may entail re-doing previous work, but full exploration of the state space is guaranteed.

While this approach makes effective use of the available memory, the running time may increase dramatically if too few states are cached. The received wisdom is that state caching is effective when the cache is larger than somewhere between 33% and 50% of the total state space, and that random replacement of states

is the best strategy. These ideas are re-investigated and found to be somewhat misleading.

We propose a new replacement strategy called *stratified caching*. Broadly speaking, it places an upper limit on the amount of redundant work that is performed when an already visited but replaced state is reached again. It does this by only replacing states at predetermined depths, or *strata*, hence the name.

Section 2 examines how state caching has been presented in the literature, and in Section 3 stratified caching is introduced and discussed. Section 4 evaluates a range of caching strategies for both random and actual state graphs, some initial results for a single model are reported in Section 5, and, finally, conclusions are presented in Section 6.

#### 2 State Space Exploration and State Caching

During state space exploration the reached states are stored in a table. When a previously visited state is reached again, it is found in the table and does not have to be re-explored. When a new state is generated and the table is full (i.e., the available memory has been exhausted), there are three possibilities:

- A. Abandon the search, explaining that the memory has been exhausted.

- B. Discard the new state and pretend that it has been seen before.

- C. Select an old state and replace it with the new state.

It is not immediately clear why possibility A would ever be preferred over B or C. Of course, it is important to notify the user that the memory has been exhausted: she may wish to interrupt the exploration and investigate alternatives. It may be that the model is faulty in some way and that the memory exhaustion is a symptom of this. Or the user may wish to investigate a simplified model, alternative options for state exploration or other reduction strategies. But it seems sensible to always continue the search with either possibility B or C. However, the implementation of possibility B or C may require memory and time overheads which the user wishes to avoid in the "default" operating mode of the state space exploration tool. Memory considerations are usually not critical since, as we shall see, state caching works well even if the cache is slightly smaller than the state space. In other words, the memory overhead may not make any real difference to the user. Time overhead is another issue and it is difficult to say, in general, whether it is wise to use or not use state caching as a default.

Possibility B results in a partial exploration of the state space, and issues such as omission probability and coverage come into play. In this case, the search may yield false positives, claiming that the model satisfies the correctness specification when, in fact, it does not, while all violations of the correctness specification are valid. As indicated in the introduction, this paper looks only at full exploration.

Possibility C is known as *state caching*, the focus of this paper. By replacing the old state, the model checker commits itself to reinvestigate the old state should it be reached again. Although this may redo work that has been done before, it does not lead to incorrect results.

State caching works well when the cache is slightly smaller than the state space. If relatively few states are replaced, the probability of revisiting a replaced state is low and even if it happens, the state's successors will probably be found in the cache. As the cache grows smaller and smaller compared to the state space, the re-exploration of states grows more and more frequent, and when the cache is very small, the problem of redundant work becomes severe. Under these conditions, the probability of revisiting a replaced state, and having to revisit its successors and their successors is high. Furthermore, each state that is revisited is re-inserted in the cache (since the depth-first algorithm cannot tell that it is not a new state) and displaces another state in the cache, in this way making matters even worse.

Depth-first search is guaranteed to terminate when state caching is used as long as states on the depth-first search path are never replaced, and the cache is large enough. Because states on the depth-first search path cannot be replaced, it is possible that too small a cache can eventually "fill up" with such states, in which case the search cannot proceed and must terminate early. (For general graphs, state caching does not work at all for breadth-first search, and offers a limited improvement in performance for mixed depth- and breadth-first search strategies; in the rest of the paper only depth-first search is considered.)

#### 2.1 State Caching in the Literature

The first discussion of state caching for model checking is by Holzmann [10]. As far as we are aware, there have been three sets of papers that report significant results about state caching.

• In [10] — which is an overview of a number of verification techniques and not an in-depth discussion of state caching — the author investigates state caching for a single model of 150000 states. States are replaced using "simple blind round robin selection", but it is not clear what data structure is used to store the states and whether all states are considered equally in the evaluation of this criterion. The conclusion of the paper is that a cache of roughly half the size of the state space can still provide acceptable performance.

In a later paper [11] (published after but written before [10]) Holzmann investigates five different replacement strategies as implemented in the *trace* tool, a forerunner of SPIN [12]. The strategies are based on replacing

- H1. most frequently visited states;

- H2. least frequently visited states;

- H3. states in the currently largest class of states, where the class of a state is defined by the number of times it has been visited;

- H4. oldest states (i.e., those states that have been in the cache longest); and

- H5. states in the bottom half of the current search tree.

As before [10], no details about how states are stored, are given. This is significant, because the data structure affects the behaviour of the state cache with respect to redundant work, memory and time consumption. The strategies

are also not clearly defined: there is no indication of how to choose between possible candidate states in strategies H1 and H2, and the "bottom half" in strategy H5 can be interpreted in a number of different ways.

The strategies are investigated "for a range of medium sized protocols". Two examples are presented, one with 4523 and the other with 8139 unique states. The paper concludes that strategy H4 is consistently the fastest (resulting in a tolerable increase in running time) even though in one of the examples it performs the most unnecessary work by far (59% "double work" compared to a maximum of 0.5% by the other strategies). No conclusions about the minimum size of the state cache are reached. Confusingly, many future references refer to H4 as "random replacement", even though it is clearly not presented as such in the paper. Also, H5 is sometimes described as replacing the state corresponding to the smallest subtree of the depth-first tree; this may be its intention, but it is not how the strategy is defined in the paper.

- Jard and Jéron investigate state caching in [13] and in [14,15]. Like the earlier work [10,11], these papers do not focus on state caching per se. In the last two works, the authors generate random graphs that are explored using depth-first search and, based on the earlier findings [11], a state cache with random replacement. They report that, in a typical case, a cache using 40% of the normal memory yields 70% more visited states and a 50% increase in running time. In the best case, the cache size is reduced to 10% of the state space with only a 1% increase in the number of visited states.

- The effect of partial-order methods [8,18,21] on state caching is addressed by Godefroid, Holzmann, and Pirottin in [7]. Sleep sets [6] is a partial-order method that eliminates most of the interleaving of independent transitions without reducing the number of states. (The combination of sleep sets and persistent sets [8], which also reduces the number of states, is further investigated by Godefroid [9].) In [6] state caching (without sleep sets) is first investigated for four models of real-world protocols using the SPIN verifier [12]. The models have a transition/state ratio of roughly 3, and the authors report that the cache can be reduced to 33% to 50% the size of the state space. These findings confirm the general results of [10,11].

The details of the state caching can be determined fully because the authors have made their software publically available. States are stored in an open hash table with pointers to singly linked lists of states with the same hash value. A state is inserted by appending it to the linked list pointed to by its hash slot. After each insertion, a check is made to see if the state store is full. If so, an old state is selected and discarded to make room for the next insertion. Although the paper claims to use a random replacement strategy, it is clear from the code that this is not entirely accurate. The linked lists are scanned cyclically and within each list the state that has been in the cache longest, and therefore occurs towards the front of the list, is always chosen first.

With sleep sets the performance of state caching improves dramatically. The transition/state ratio of one model decreases from 2.88 to 1.45 and a cache of about 25% the size of the state space suffices. For the other three models, the

use of sleeps sets reduces the ratio from 2.80, 3.54, and 2.58 to 1.12, 1.04, and 1.04, respectively. For these, the cache performs spectacularly well: a cache size of only 0.2% to 3% the size of the state space suffices for a complete exploration of the models. Unfortunately, the running time increases by a factor of between 2 and 4, but it is not clear whether this is caused by the implementation of the sleep sets or the state caching.

### 2.2 Other Work Related to State Caching

The performance of state caching using open addressing — also known as closed hashing — has also been investigated [5,19], but, due to space constraints, this approach is not considered here. Other techniques that may improve the effectiveness of state caching have been suggested, sometimes in more general contexts. This includes the identification of states to replace preferentially [7, 10], heuristic state space exploration [4], probabilistic caching of states [3], and precomputation to enhance replacement strategies [17].

### 3 Stratified Caching

When a state cache contains only a few replaced states, the probability of revisiting a deleted state is small, the probability that the state has a deleted child is smaller, the probability that the child also has a deleted child is smaller still, and so on. As the number of replacements grows, these probabilities increase to the point where practically every deleted state has at least one deleted child, and most states have several. Revisiting a deleted state in this situation leads to a considerable amount of redundant work; not only do large subtrees require re-exploration, but each revisited state is also re-inserted in the cache, pushing out yet another state, and causing a cascade of revisits.

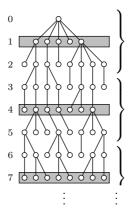

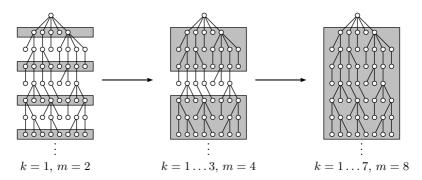

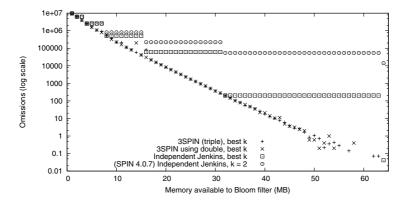

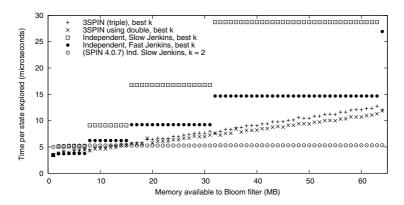

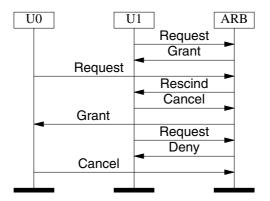

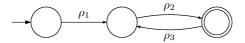

Stratified caching limits the redundant work by placing an upper bound on how much deeper than usual each branch of the depth-first tree needs to be explored, hereafter referred to as the *extra depth*. It does this by only replacing states at specified levels of the depth-first search tree. All states at a certain level form a "stratum" of states.